Product Summary

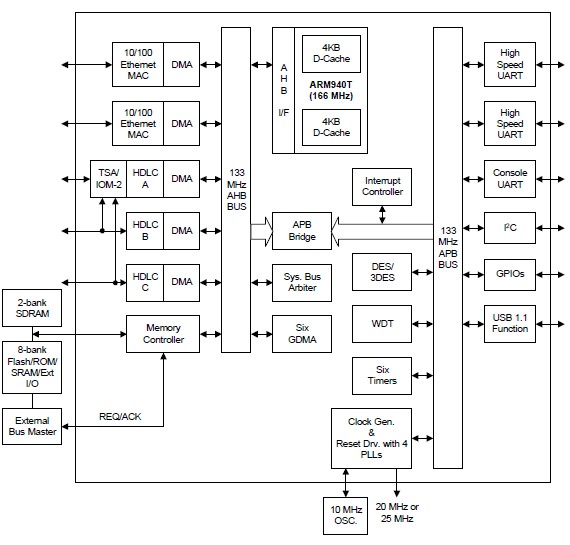

The S3C2500B01-GAR0 is a 32-Bit RISC Microprocessor. The S3C2500B01-GAR0 16/32-bit RISC microcontroller is a cost-effective, high-performance microcontroller solution for Ethernet-based systems, for example, SOHO router, internet gateway, WLAN AP, etc. A variety of communication features is embedded into S3C2500B01-GAR0 required in many communication areas, including two Ethernet MACs, three HDLCs and three TSAs supporting IOM2, two high speed UARTs, a console UART, and USB. A security feature is also supported by DES/3DES accelerator. This highly integrated microcontroller enables customers to save system costs and increase performance over other 32-bit microcontroller.

Parametrics

S3C2500B01-GAR0 absolute maximum ratings: (1)VDD DC supply voltage: 1.8V VDD: 2.7 V, 3.3V VDD: 3.8V; (2)VIN DC input voltage: 3.3V; (3)VOUT DC output voltage: 3.3V; (4)ILATCH Latch-up current: ± 200 mA; (5)TSTG Storage termperature: - 65 to 150 ℃; (6)CIN Input capacitance Any Input Bi-directional Buffers: 4 pF; (7)COUT Output capacitance Any Output Buffer: 4 pF.

Features

S3C2500B01-GAR0 features: (1)Fully 16/32-bit RISC architecture.; (2)Harvard cache architecture with separate 4KB Instruction and Data cache; (3)Protection unit to partition memory and set individual protection attributes for each partition; (4)AMBA Bus architecture; (5)Up to 166MHz operating frequency; (6)24-Bit External Address Pins; (7)2 Banks for SDRAM with 16/32-bit external bus; (8)8 Banks for Flash/ROM/SRAM/External I/O with 8/16/32-bit external bus; (9)One External Bus Master with Bus Request/Acknowledge Pins.

Diagrams

|

S3C2400 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C2410A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C2410X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C2412XL-26 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C2440A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C2440A-40-YQ80 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))